Quick

Quick

I discover this on the website https://www.tensorflow.org/tutorials/keras/save_and_restore_models ```python (train_images, train_labels), (test_images, test_labels) = tf.keras.datasets.mnist.load_data() train_labels = train_labels[:1000] test_labels = test_labels[:1000] train_images = train_images[:1000].reshape(-1, 28 * 28) / 255.0 test_images =...

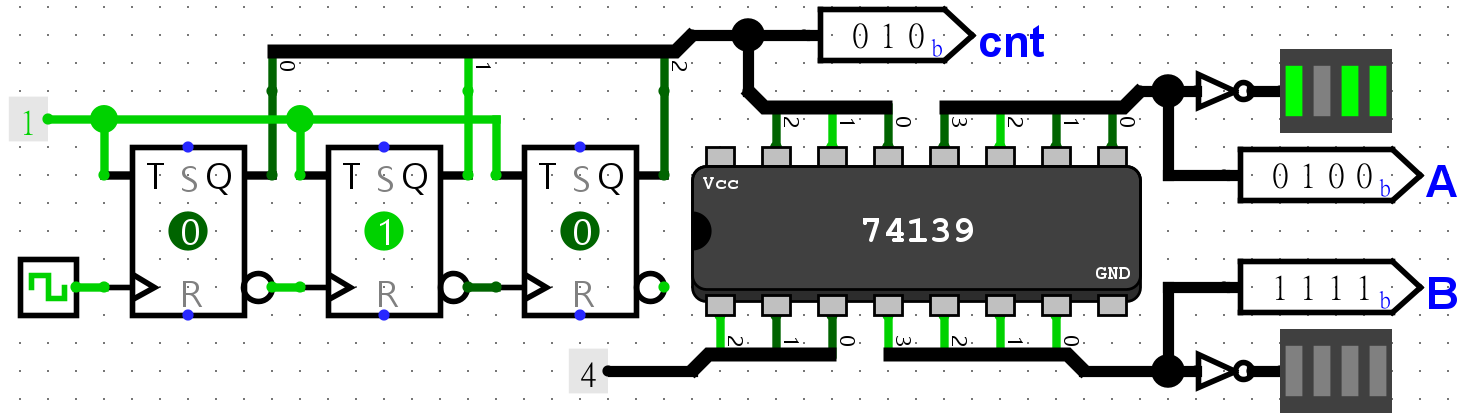

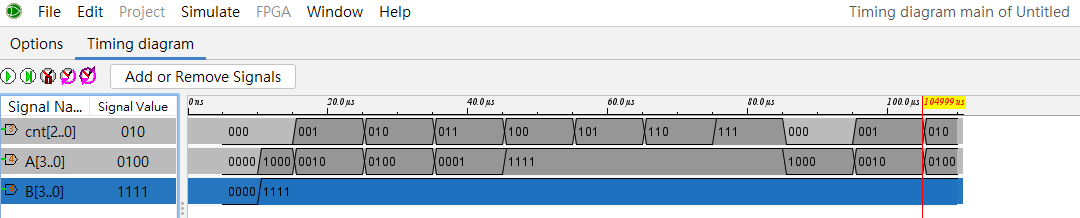

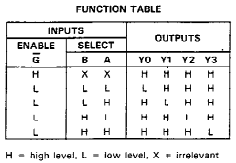

I just try to do some experiment on 74139 [74LS139 datasheet](https://www.futurlec.com/74LS/74LS139.shtml) Screenshot of the datasheet:   Test Circuit:  Timing Diagram:

Seems like the inputs are ok only need to invert the output

Sorry I missed that. I also checked the [datasheet](https://www.ti.com/product/SN74LS139A) mentioned in code. It still said the same thing  (I tested in `develop` branch)

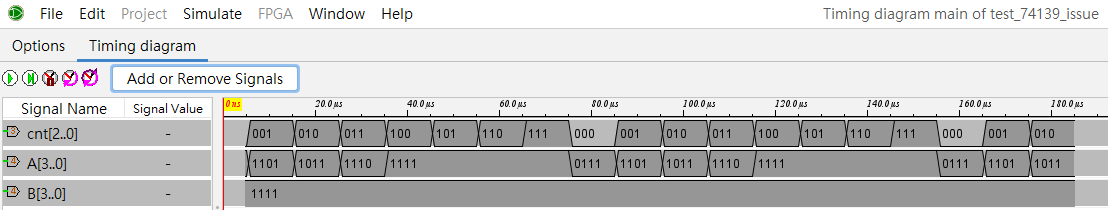

I tried to put some fix (tested with same *.circ file)  better

https://github.com/logisim-evolution/logisim-evolution/blob/master/src/main/java/com/cburch/logisim/std/ttl/Ttl7485HdlGenerator.java#L59-L59 For this line mentioned by OP, it should be changed to `Hdl.isVhdl()` https://github.com/logisim-evolution/logisim-evolution/blob/master/src/main/java/com/cburch/logisim/fpga/hdlgenerator/Hdl.java#L39-L45

I think that #297 is simple enough, however I guess something like adding `vendor/` into `.gitignore` needs to be considered.

Just for reference, #257 is closed, but I can't see a discussion in the PR, I guess we need more consideration on the disadvantage of deleting `vendor/` folder. (Just to...

> we're having a discussion in #284 I see, thanks!