Jack Cheng

Jack Cheng

Add GPIO

I want to add GPIO in block design, I did: 1. make CONFIG=rocket64b2 BOARD=genesys2 vivado-gui 2. Add AXI GPIO in blkck design, validate and synthesize the design 3. Make sure...

If want to use peripheral on fpga These three steps are based on your description 1.add IP to block design and program to FPGA 2.add peripheral to device tree 3.enable...

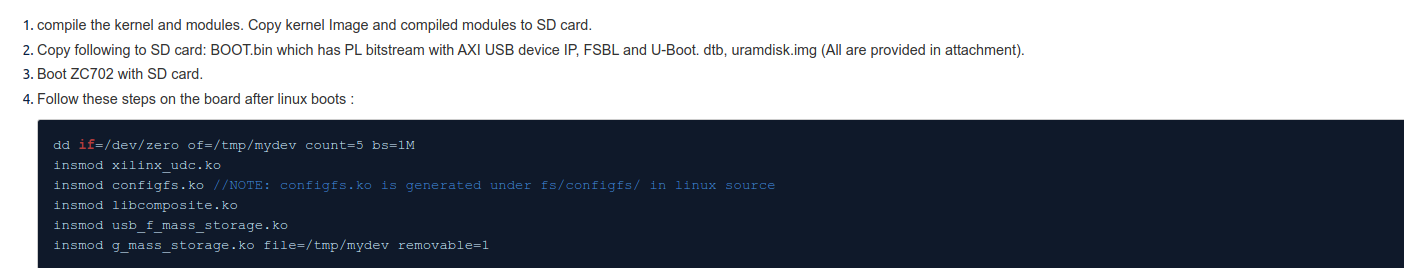

> I want to enable genesys2 USB device > will the linux kernel object(.ko) be generate in linux-stable?

I want to enable my USB device on FPGA I add AXI USB2 device in Vivado Do I just need to use the udc-xilinx.c as driver? or need other config?...

https://people.eecs.berkeley.edu/~ysshao/assets/papers/genc2021-dac.pdf In this paper, I observed that Gemmini includes the im2col module. The Rocket core consumes too many clock cycles on im2col. I need a more efficient way to execute...

HI, I want to read clock cycle by function "read_cycles();" This function is work on spike simulation, like this:  but when I run file-linux on genesys2, the clock cycle...

I tried to put this usb host ip into my FPGA (genesys2), during the linux boot process, it stuck on the driver, I added some strings to the driver to...

The upli_data_io[7:0] in the ulpi interface is composed of ulpi_data_i, ulpi_data_o and ulpi_data_t. Why is there no ulpi_data_t in the ulpi interface here?

Hi, I'm a SteamVR user and I'm using CloudXR to connect my PC and VR headset via Wi-Fi. Recently, we've noticed that during gameplay, the VR headset unexpectedly exits CloudXR...