can not recognize constant

Describe the bug recognize constan that is not in length of value as error

To Reproduce

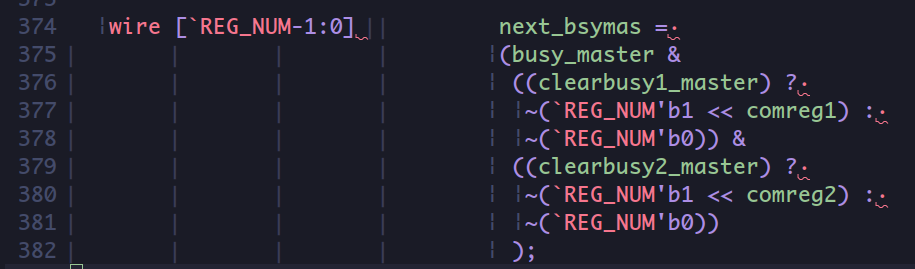

verilog:

report:

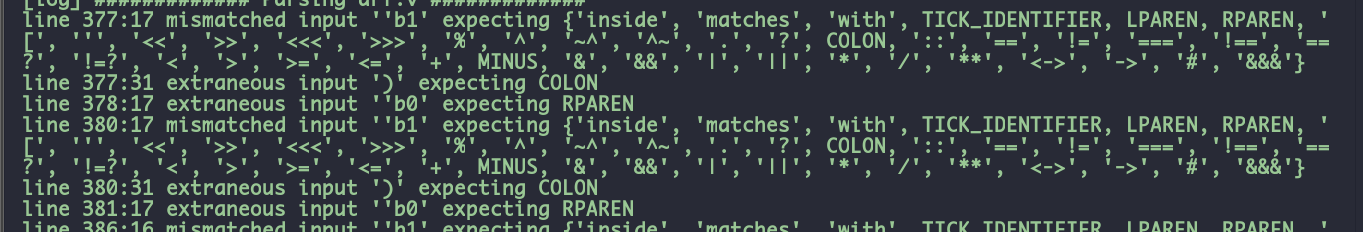

report:

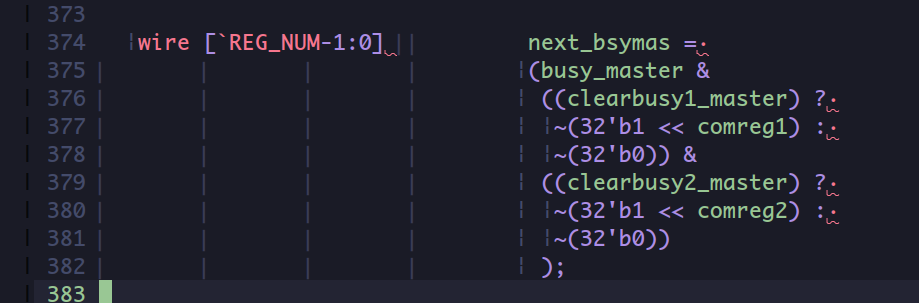

verilog without constants:

verilog without constants:

report:

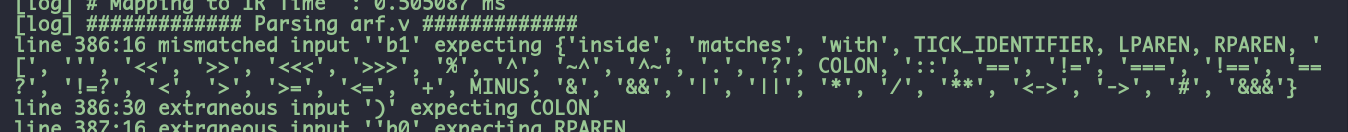

report:

if not use

if not use reg_num, the report not print and the lines that still use reg_num, its reports still print

Expected behavior A clear and concise description of what you expected to happen.

Additional context Add any other context about the problem here.

Hi @HaibaraMegumi

Thank you for your interest in sv2chisel and for your bug report.

I have just realized there is no test-cases involving macros (we have migrated our code-base to packages a while ago) which hides an unfortunate reality: macros are really badly supported and translated!

I will work on a basic macro support and keep you updated.

PS: for easier bug reporting you can use the code balise of github https://docs.github.com/en/get-started/writing-on-github/working-with-advanced-formatting/creating-and-highlighting-code-blocks

```verilog

// minimal reproducing example

wire [`TRUC-1:0] test = `TRUC'b1;

```

would be displayed as

// minimal reproducing example

wire [`TRUC-1:0] test = `TRUC'b1;

Just pushed 0.5.1-SNAPSHOT with very minimally improved support for preprocessing macros. See https://github.com/ovh/sv2chisel/commit/c0cfcd0153750cecb7c14b5109ab627a0271cad1

This won't unfortunately solve the underlying deficient support for macros but at least you should be able to proceed beyond the lexing/parsing step.

Adding a real support for macros in sv2chisel is a considerable work and it would require an actual (open-source?) project based on intensive use of such macros to be able to implement a consistent translation. Note that by construction, translating meta-programming constructs into a plain uniform language (even scala) is only achievable on a rather restricted number of well-identified patterns.