make c5socarm project compatible with quartus16.1

In casse the openPowerlink-projects decides to switch to more recent versions of the altera development tolls / quartus one day, this could patch could be used to get an idea what changes were nescessary for us in order to get it working with Quartus-16.1 (although with a custom board, so the excact configuration shipped has not been tested).

Hello Ceisserer,

We have validated your pull request with the below configurations:

-

PC - Windows 7

-

Altera Quartus II - 16.1

-

Target platform - Altera C5 SoC

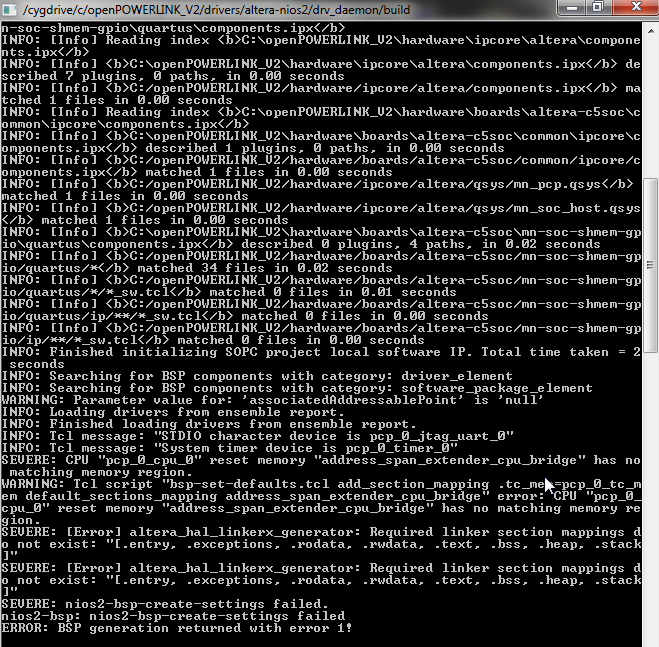

We found that the Altera C5 SoC hardware build is successful, but the BSP build is failing. Please find below the error message screenshot.

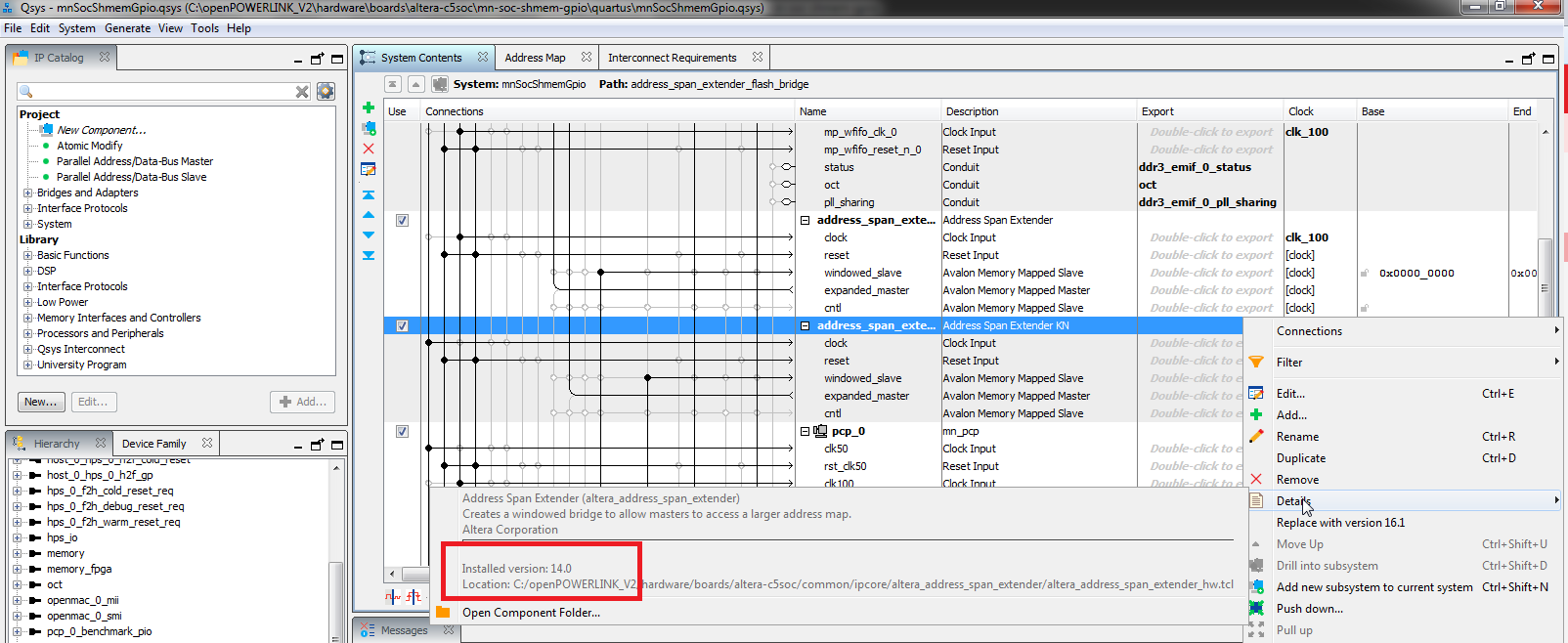

Note: We also see that the "Address Span Extender" IP core is set to version 14.0 by default. We have upgraded the IP core version to 16.1 and re-validated the design, but the problem exists.

Because of relocation I've changed my employer and am no longer working on openPowerlink. I've reached out to my former colleagues regarding this open pull request.

BSP Generation for the Nios II driver daemon fails, because no region information is available for address_span_extender_cpu_bridge. As described by NIOSII using the FPGA-to-HPS SDRAM Bridge via Address Span Extender, this can be resolved either by editing the generated .sopcinfo file or by uncommenting two lines in <QUARTUS>/ip/altera/merlin/address_span_extender/altera_address_span_extender_hw.tcl:

set_interface_assignment windowed_slave embeddedsw.configuration.isMemoryDevice 1 set_interface_assignment windowed_slave embeddedsw.configuration.affectsTransactionsOnMasters "expanded_master"